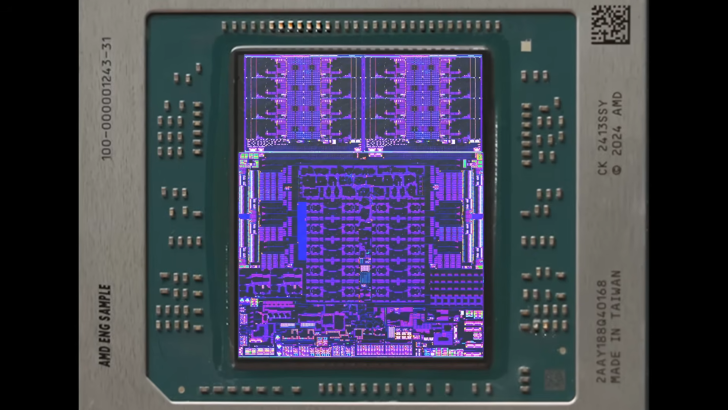

AMD Switches to 'Sea-of-Wires' Interconnect for Next-Gen Zen 6 CPUs

AMD is shifting from SERDES-based die-to-die interconnects to a 'Sea-of-Wires' fan-out approach in Zen 6 CPUs, inspired by Strix Halo APUs, which reduces power and latency while increasing bandwidth, marking a significant upgrade in interconnect technology.